利用 ASIC 重构,提高网络效率 -- ASIC功耗和散热在现代网络中的重要性

作者:Chang-Hong Wu,

VP Juniper Fellow, Networking Silicon Architect and Technologist

翻译: Shawn Zhang, Juniper Consulting System Engineer

穿越网络的每一位bit信息,在从源头到目的地的路径上,通常都要多次经过网络系统设备中的 ASIC 来交换实现。因此,ASIC 功耗和散热对于保持网络高效至关重要。 ASIC的高功耗和同时产生的高热量,需要复杂的电源和高容量的风扇来进行冷却,而这些风扇本身又有更大的功耗,使问题更加复杂。

多年来,半导体制程技术的改进一步一个脚印,进展顺利。正如戈登·摩尔(Gordon Moore)在著名的摩尔定律中所描述的那样,半导体技术大约每 18 个月左右改进两倍。如果某一代ASIC性价比太低、散热不理想,亦或不够快,您可以等待下一代制程的半导体技术,然后在技术浪潮中获得更快、更便宜、更低功耗的 ASIC来实现。在网络系统一代一代的迭代中,仍然需要做很多艰苦的工作,但您仍从新技术本身中受益很多。

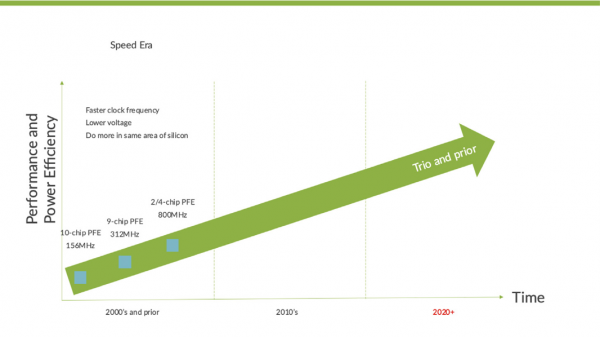

这正是本世纪前十年及之前发生的事情。如图 1 所示,每一代的网络技术都通过以更高的时钟速度和更少的芯片数量来改进带宽、功能和功率。一个例子就是 ASIC 在这十年之初以 156MHz 开端,以大约 800MHz 终结,大概增加了 5 倍,但构成芯片组的 ASIC 数量却从 10 个减少到 2 个。这是一个“以速度为代表的时代”(Speed Era),我们通过更快的运行速度和更少的总硅面积实现了更高的带宽、更好的功能和更低的功耗。在2009年,瞻博网络在 MX 通用路由平台中引入了 Trio ASIC。这是一组非常灵活和可编程的 ASIC 和系统,在高性能的同时,基本上可以提供当时大部分网络的功能需求。

图1: Speed Era (以速度为代表的时代)

然而,在这十年的后几年,半导体改进的步伐显示出放缓的迹象。虽然随着每一代制程技术的发展,逻辑门的密度仍在增加,但工作电压的降低以及内在功耗的进步基本上都停止了。随着几何尺寸越来越小,晶体管的本征性能也没法在不影响功耗的前提下有很大的改进。这一趋势在接下来的几年中一直持续到 2010 年代。与此同时,随着视频业务的日益普及和运营商及OTT大型数据中心的出现,带宽的需求与日俱增,这对更高带宽和更节能的网络产品提出了更高需求。

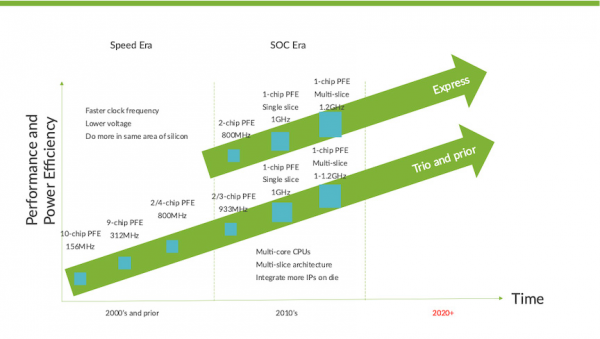

在瞻博网络,我们注意到 ASIC 的片外访问(Off-Chip Accesses)正在成为实现高带宽的瓶颈,而且off-chip比on-chip连接消耗更多的功率。基于这种认识,我们推出了Express ASIC芯片和 PTX 核心路由平台。用一系列的新技术,包括虚拟输出队列(VoQ)和基于散列的最长前缀匹配查找(hash-based longest-prefix-match lookup ),我们将片外数据包缓冲区访问次数减少了一半,查找转发表访问减少了大约5倍。因此,通过优化这些特定网络应用平台,以及创新架构技术,我们在同一代的半导体技术中,将最终产品的功耗效率提高了大约两倍,如图2所示。

图2: SOC 时代

随着芯片到芯片之间带宽和互连的增加,互连所消耗的功率在整个芯片组功率中所占的比例越来越大。我们和业界同行合作,瞻博网络 ASIC 率先使用具有高速串行接口的 3D 存储器,从而将所有数据包转发、排队和接口功能集成到单个芯片中。在2010 年代的后半段,瞻博网络是最早采用“内封装高带宽内存 in-package HBM” 的网络供应商之一,更进一步,将多个slices和多个处理内核cores整合到同一个裸片上。这些创新技术,显著降低或去除了由于外部互联导致的高功率需求,同时也提升了带宽、降低能耗。这十年的进步主要体现在,虽然逻辑速度并没有太大的提高的同时,但在同一个芯片上集成了更多的功能。这就是为什么我将这十年称为“SOC 时代”或片上系统(System on a Chip)。

然而,使用“SOC 时代”的技术导致芯片尺寸越来越大。事实上,在这十年的尾端,很多的网络 ASIC 已接近现有半导体制造工艺可以容纳的最大尺寸。此外,在纳米级半导体制程中,杂质缺陷的出现是一种自然现象。一旦裸片尺寸达到一定阈值,从制程中获得无缺陷芯片的概率呈指数级下降,从而使良品的成本增加。显然,SOC 方法不可能永远持续下去。我们必须寻找更新的,可替代的方案。

近年来,该行业正在采用一种新方法,有时被称为“超越摩尔 More Than Moore”方法。这种方法,既不是在 PCB 上使用几个单独的 ASIC(从而增加芯片之间的互连功耗),也不是将所有都集成在一个芯片上(从而牺牲成本),而是将多个尺寸合理的芯片放在同一个封装内,每个芯片都用相对优化的制程工艺,实现本地的低功耗互连。这样即可以保持提升系统的功能和性能,又同时优化能源成本。这正可能是 2020年代的新解决方案。请参见图 3。

图 3: SiP(System in a Package)时代

瞻博网络将继续推出创新架构和集成技术,和我们的伙伴通力合作,并在这个新的“SiP(System in a Package)时代”提高产品的经济性和能效。

好文章,需要你的鼓励

Queen‘s大学重磅研究:程序员的角色即将彻底改变,从码农到智能体指挥官

Queen's大学研究团队提出结构化智能体软件工程框架SASE,重新定义人机协作模式。该框架将程序员角色从代码编写者转变为AI团队指挥者,建立双向咨询机制和标准化文档系统,解决AI编程中的质量控制难题,为软件工程向智能化协作时代转型提供系统性解决方案。

苹果发布 iOS 26.0.1 系统更新,修复多项关键问题

苹果在iOS 26公开发布两周后推出首个修复更新iOS 26.0.1,建议所有用户安装。由于重大版本发布通常伴随漏洞,许多用户此前选择安装iOS 18.7。尽管iOS 26经过数月测试,但更大用户基数能发现更多问题。新版本与iPhone 17等新机型同期发布,测试范围此前受限。预计苹果将继续发布后续修复版本。

医疗AI的“显微镜革命“:西北工业大学团队发布首个超声影像专用智能助手EchoVLM

西北工业大学与中山大学合作开发了首个超声专用AI视觉语言模型EchoVLM,通过收集15家医院20万病例和147万超声图像,采用专家混合架构,实现了比通用AI模型准确率提升10分以上的突破。该系统能自动生成超声报告、进行诊断分析和回答专业问题,为医生提供智能辅助,推动医疗AI向专业化发展。

业界首款符合AEC-Q200标准额定电压高达1,000 VDC高压保险丝

数据中心的智算挑战,英特尔要如何应对?

下一代智能工厂怎么建?开放自动化给出“解题思路”

跟随西门子,在工博会感受沉浸式的工业AI体验

苹果发布 iOS 26.0.1 系统更新,修复多项关键问题

OpenAI将发布类似TikTok的社交应用,搭配Sora 2视频模型

微软推出Office智能体模式让用户"氛围办公"

AI助手现在能帮你创建高质量Word文档和Excel表格

高通新一代骁龙平台将推动智能体AI时代到来

SAPx阿里云,开启一条通往中国市场与全球化发展的全新路径

微软推出"氛围工作"模式,为Office套件加入AI智能体

OpenAI推出智能购物系统挑战谷歌亚马逊

十年一剑,TPU引领AI芯片时代

瞻博网络推出业界首款AI原生网络平台,创造卓越用户体验,大幅降低运营成本

瞻博网络推出全新Beyond Labs计划, 以求解决“体验至上的网络”时代的最大挑战

借助大型语言模型能力、Zoom集成和更多Wi-Fi 6E产品, 瞻博网络进一步提升AIOps领导地位

瞻博网络推出首款Mist AI驱动的云原生访问保障服务

瞻博网络SRX4600防火墙在独立企业网络防火墙测试中获得推荐评级

瞻博网络推出园区网架构3步流程和新款EX分布式交换机,为企业带来更加简单、安全和规模化的网络

瞻博网络2023年新计划助力合作伙伴网络业务取得更大成功

瞻博网络连续第三年获评Gartner 企业有线和无线局域网基础设施魔力象限领导者

汉基国际学校选用瞻博网络人工智能解决方案 提升学生数字学习体验