ASIC 关键字列表

2024-11-01

十年一剑,TPU引领AI芯片时代

TPU 的设定,只能在 TensorFlow 中执行推理,但它的性能非常好。我们认为,TPU 与 TensorFlow 的良好适配,能够发挥出 1+1>2 的效果。深度学习计算中的芯片部署都不是零和博弈。现实世界的深度学习网络需要系统的 GPU 与其他 GPU 或诸如 Google TPU 之类的 ASIC 通信。GPU 是理想的工作环境,具有深度学习所需的灵活性

利用 ASIC 重构,提高网络效率 -- ASIC功耗和散热在现代网络中的重要性

如果某一代ASIC性价比太低、散热不理想,亦或不够快,您可以等待下一代制程的半导体技术,然后在技术浪潮中获得更快、更便宜、更低功耗的 ASIC来实现。在网络系统一代一代的迭代中,仍然需要做很多艰苦的工作,但您仍从新技术本身中受益很多。

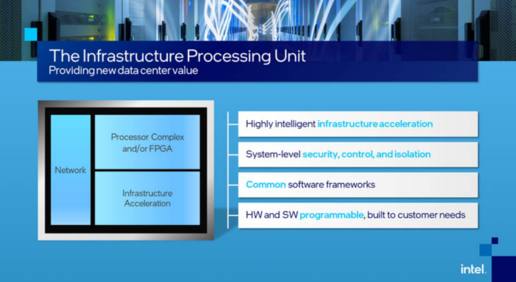

英特尔坚持在下一代IPU中使用FPGA与ASIC

在本周召开的Intel Vision大会上,英特尔再次强调了其双管齐下的ASIC/FPGA基础设施处理单元(IPU)发展战略。此次会上,英特尔还展示了即将推出的400 Gb/秒与800 Gb/秒设备。

英特尔发布首款用于5G、人工智能、云端与边缘的结构化ASIC

在英特尔FPGA技术大会上,英特尔发布了全新可定制解决方案英特尔eASIC N5X,帮助加速5G、人工智能、云端与边缘工作负载的应用性能。